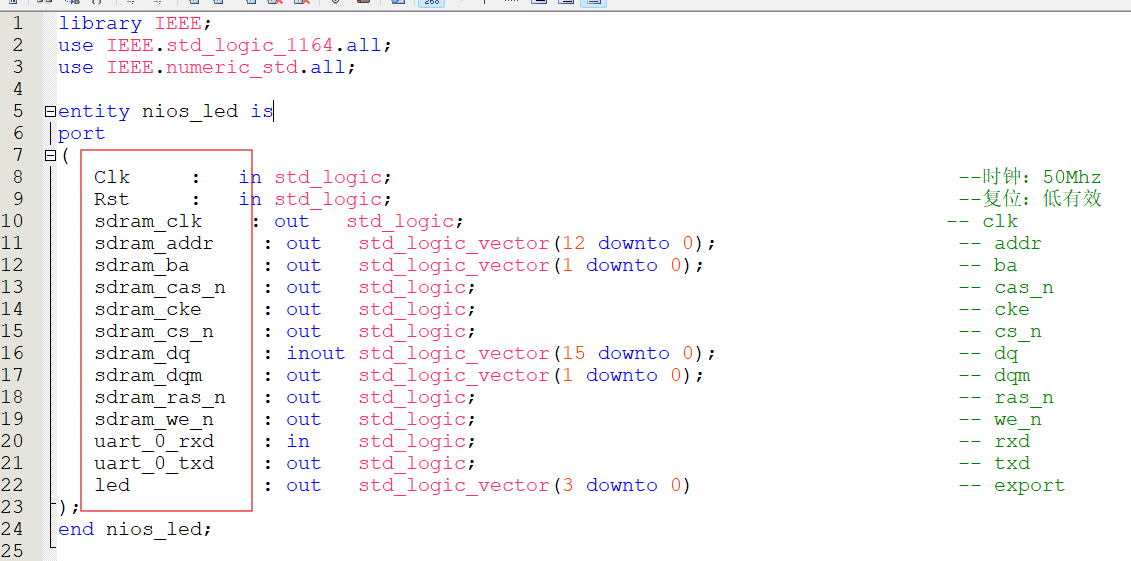

前面经过了工程创建、软核配置、时序约束、工程编译,这一节主要进行FPGA管脚的分配与配置。FPGA芯片有大量的管脚,这些IO基本都是通用的,可用作输入、输出,或者自定义接口。

所以,我们在定义实体时声明的那些信号,要分配到相应的管脚。

操作步骤如下:

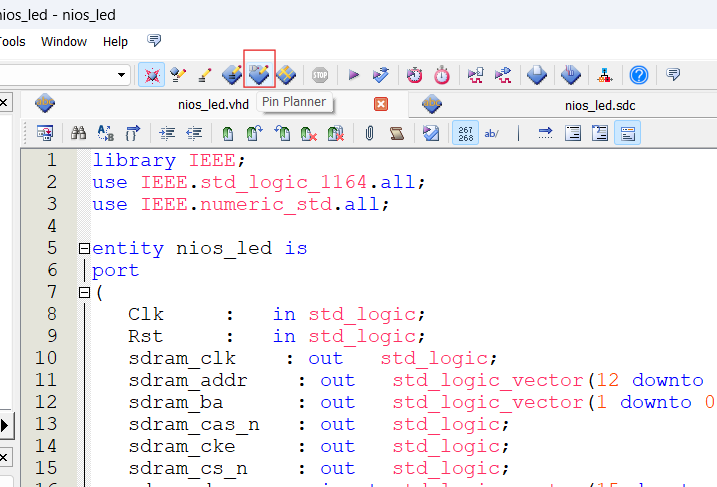

一、打开快捷按钮Pin Planner

打开后,调整管脚区域的大小。尽量放大,方便后续操作。效果如下:

二、修改IO工作电平

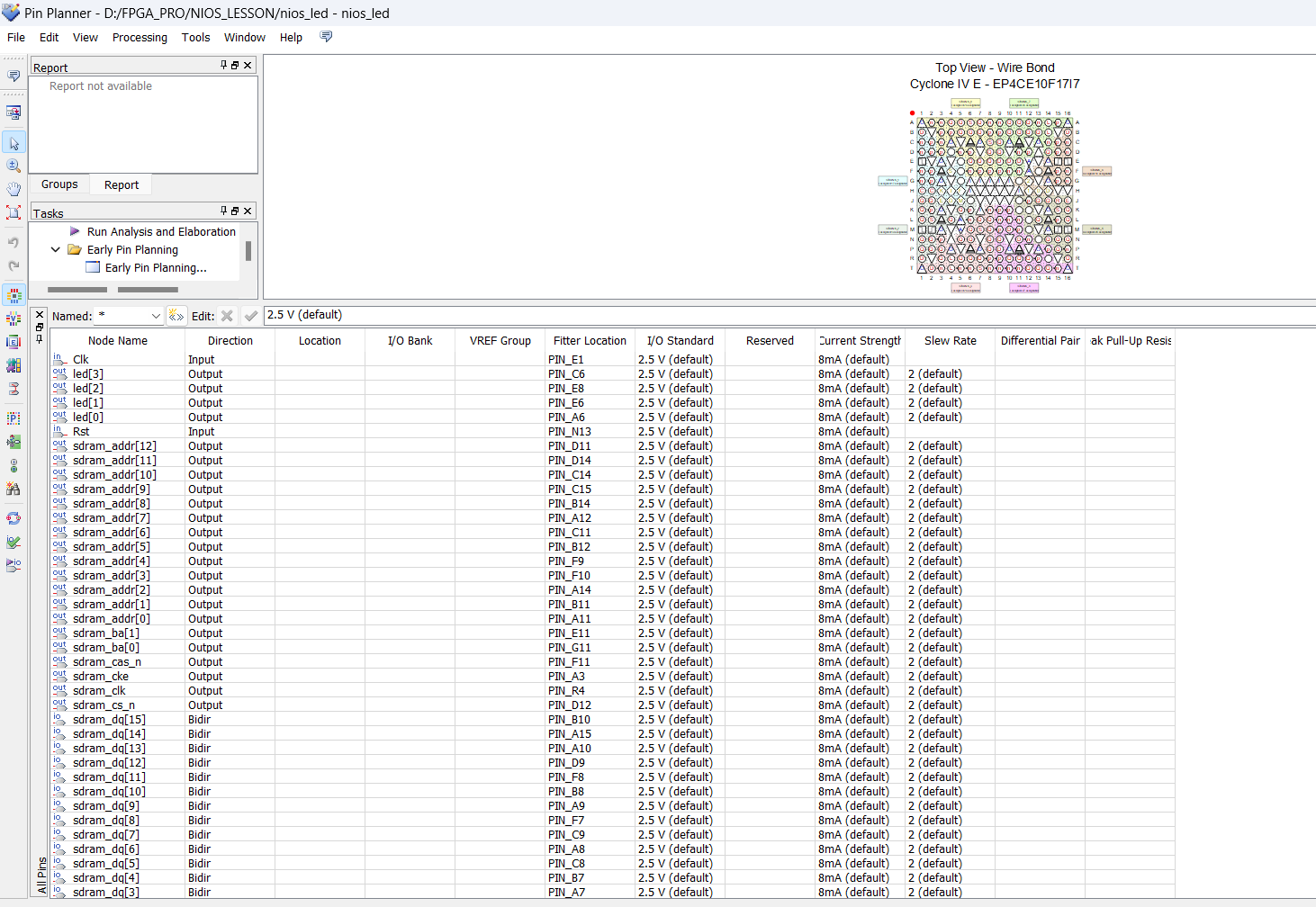

在I/O Standard那一列,显示IO的工作电压都是2.5V。实际电路中的工作电压是3.3V,所以要修改。

双击2.5V,改成3.3V ,如下:

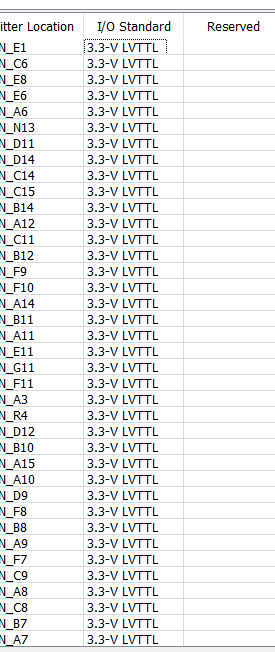

然后选中3.3那一格,ctrl+c,复制一下。然后选中下面所有的2.5,ctrl+v,粘贴一下。效果如下:

三、分配IO位号

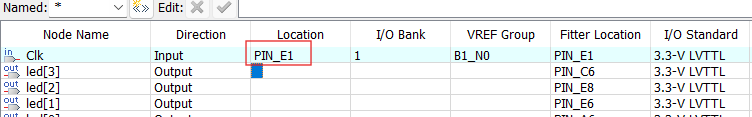

给每个信号,分配一个指定的FPGA管脚。例如clk信号,AC601模块中,时钟信号接到了E1管脚上,那么这里就在Clk对应的location那里输入:e1,剩下的它会自动补齐,然后敲回车即可。

效果如下:

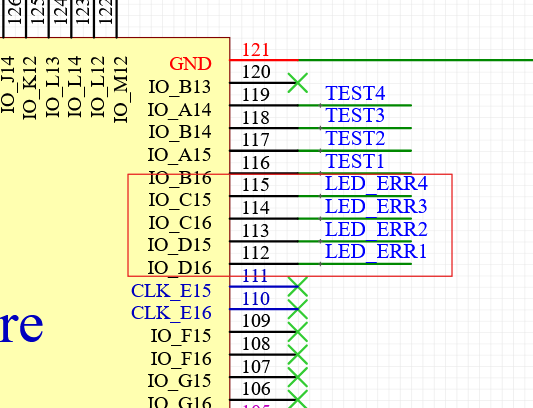

然后是4个LED,这里我画图时接到了C15、C16、D15、D16这四个管脚,如图:

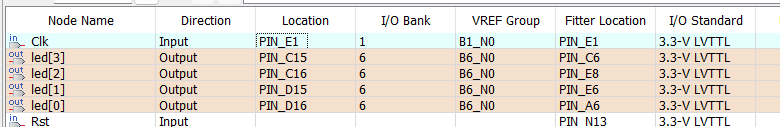

分配后:

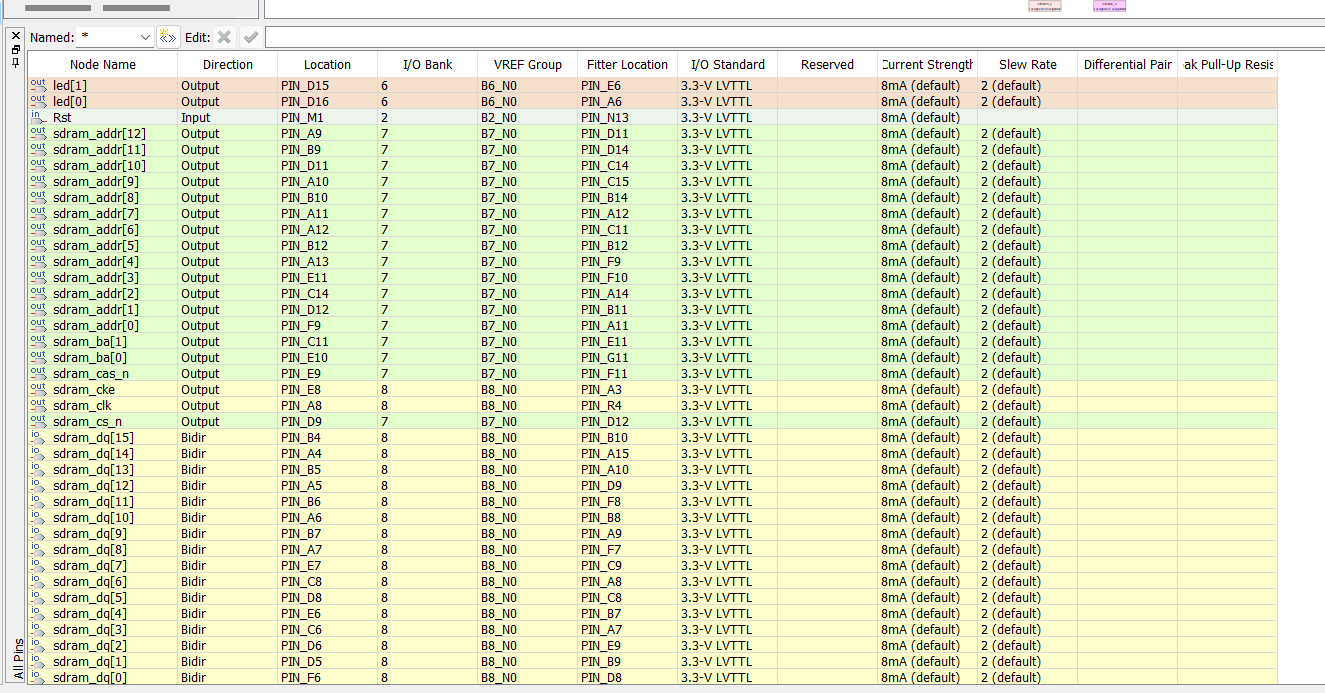

剩下RST信号,SDRAM接口,UART接口,依次分配,最后效果如图:

检查无误后,关闭页面。

四、Device and Pin Options配置

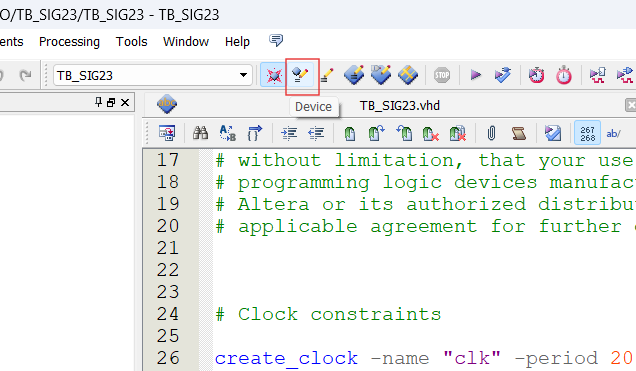

把闲置端口配置为输入、三态。点击菜单栏快捷键:Settings。弹出如下窗口:

弹出窗口如下,点击其中的:Device and Pin Options。

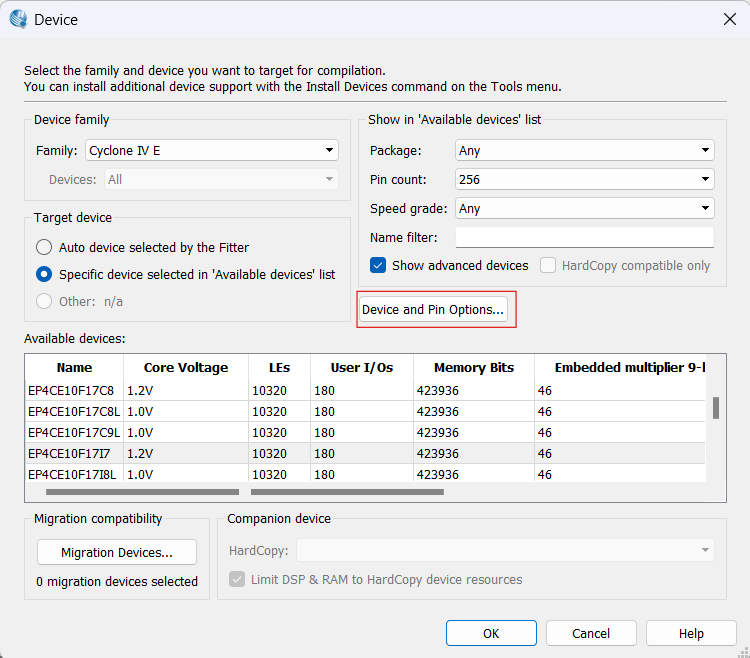

4.1 Dual-purpose Pins设置

弹出Device and Pin Options页面,默认选中了:Dual-purpose Pins选项。双击修改右侧的管脚Value选项。全都改成:use as regular I/O,如下图样式:

先不要关闭。

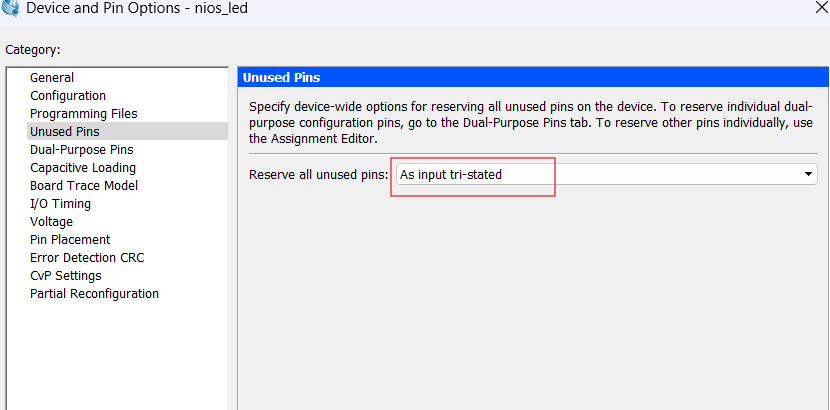

4.2 Unused Pins 配置

闲置管脚配置,选中左侧的:Unused Pins,在右侧的下拉选项中,选择如下所示。

通过这种方式,把闲置管脚配置为输入模式,三态。点击OK,保存。

五、编译

再次编译,等待编辑结束。至此,我们创建了一个带有NIOS II软核的FPGA工程,并分配好了管脚,做好了最终编译。

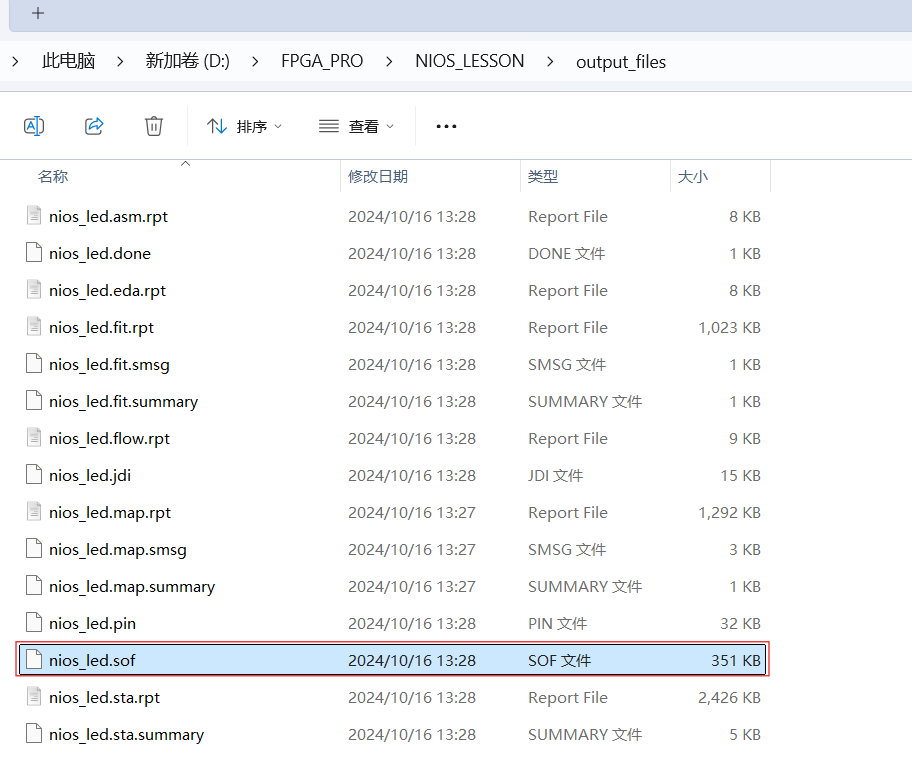

生成了一个可以烧录的文件:

但是,这个软核里面现在是空的,还没有对其写入程序。具体操作下一节见!