上一节完成了NIOS II软核的创建、编译。这一节把它加入到FPGA的工程中,实现FPGA内包括一个CPU的效果。

一、包含软核文件

上一节最后,生成了软核文件:core_led.qsys。虽然是在nios_led工程内生成的,但是和这个工程没有直接的关联。所以要先把软核文件添加到工程中。

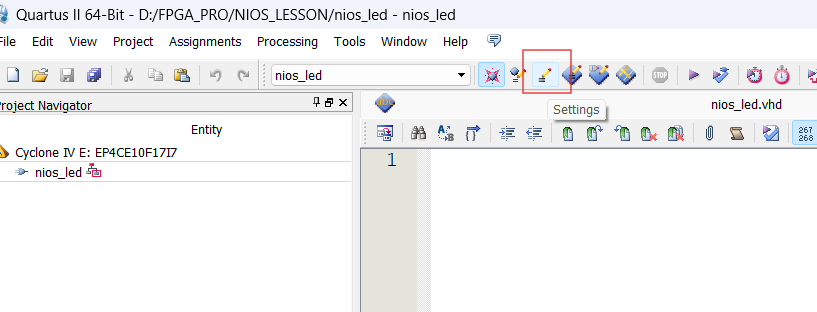

点击quartus ii上面的Settings,在弹出的对话框中,添加软核文件。

添加步骤如下:

最后点击OK关闭即可。

二、编写VHDL部分代码

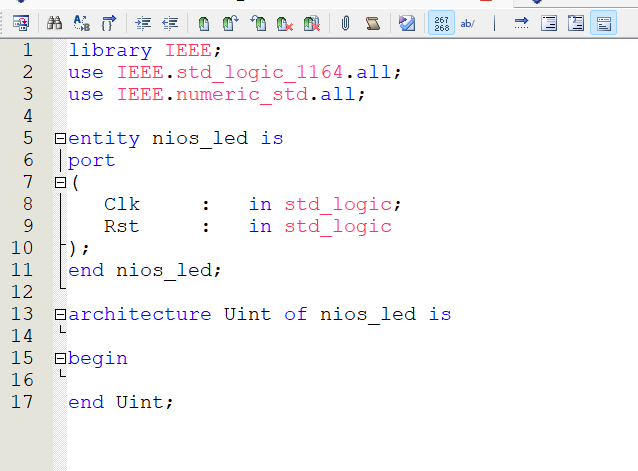

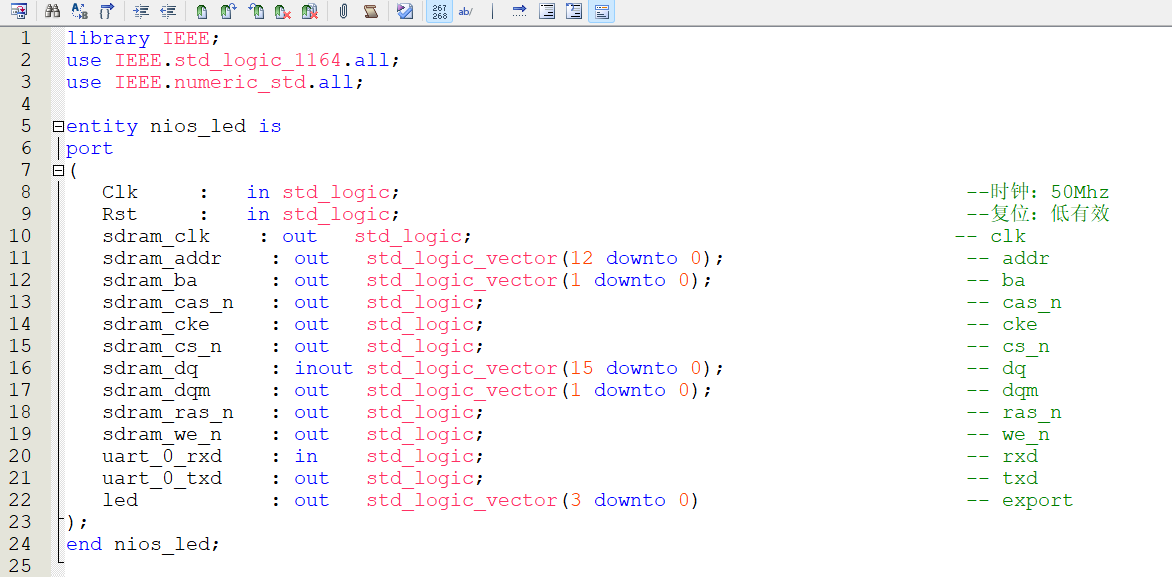

添加一些头文件,然后创建一个实体,实体名称一定要和工程名称一样。效果如下:

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity nios_led is

port

(

Clk : in std_logic; --时钟:50Mhz

Rst : in std_logic --复位:低有效

);

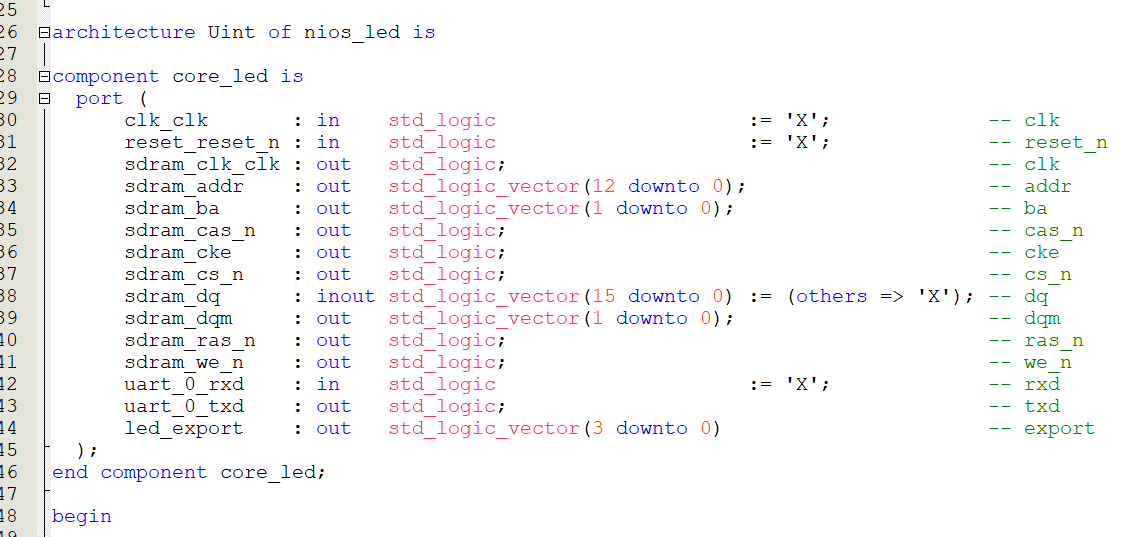

end nios_led;然后,声明一个architecture块,定义设计的结构和行为。整体效果如下:

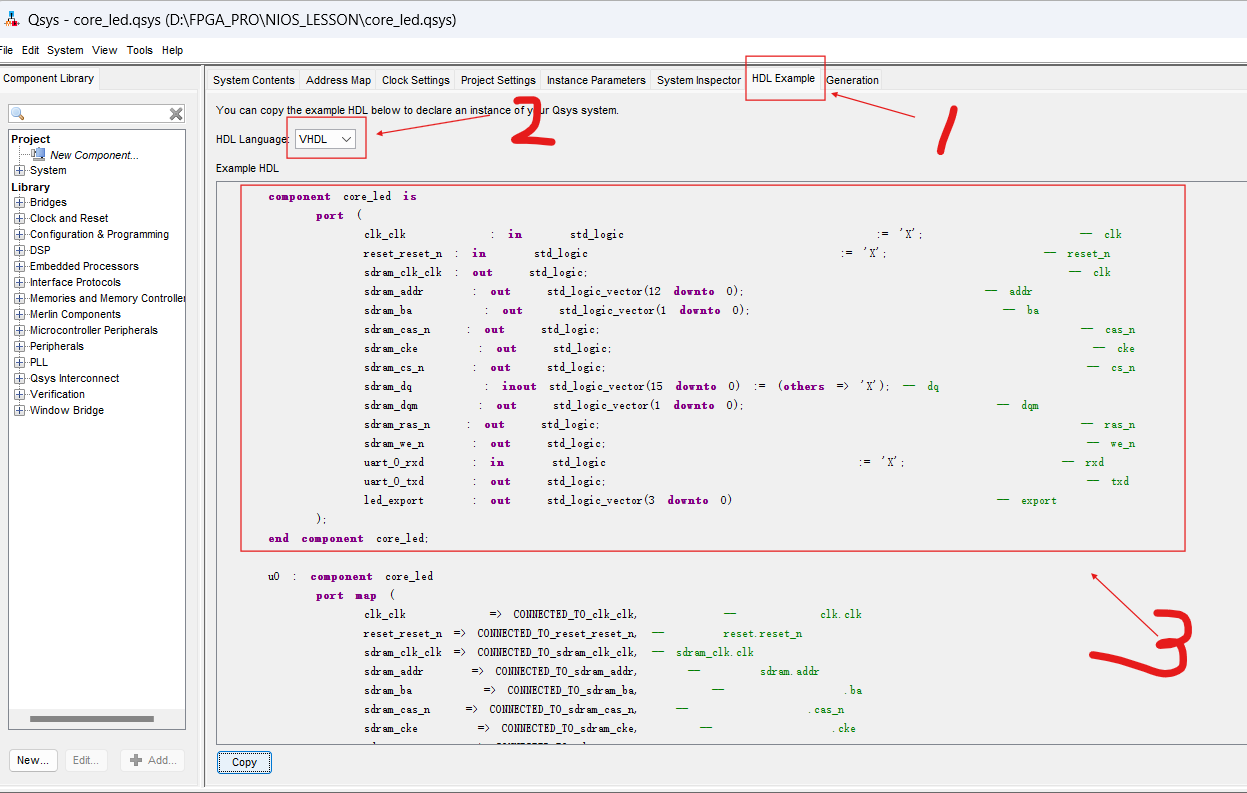

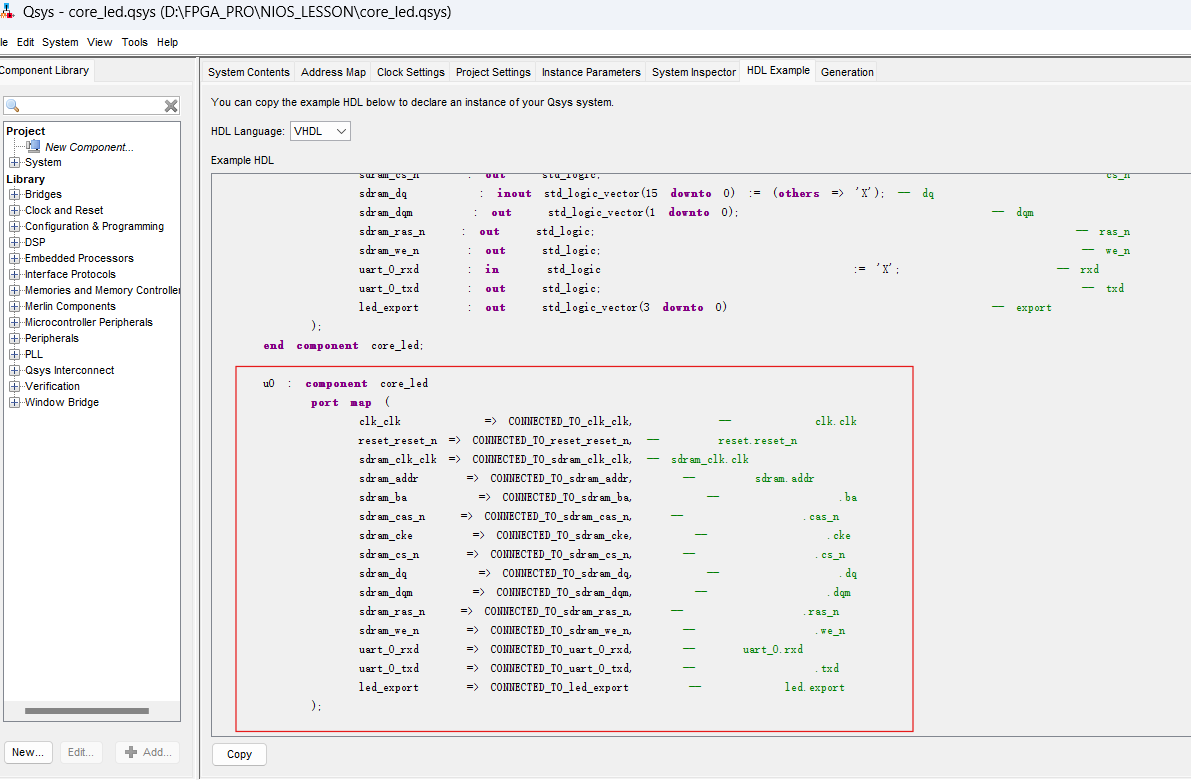

接下来,基于软核,定义并实例化一个组件,命名为:core_led。打开Qsys,打开上一节生成的软核文件。

如图所示,先点击HDL_Example,切换选项卡,然后修改语言为VHDL,最后复制步骤3对应的红框的内容,粘贴到niso_led.vhd文件中,进行组件的定义。位置在architecture之后,begin之前。

粘贴后,进行一些格式对齐的工作。最后效果如下:

然后,复制如下区域代码到实例化区域中,调整格式并修改接线。

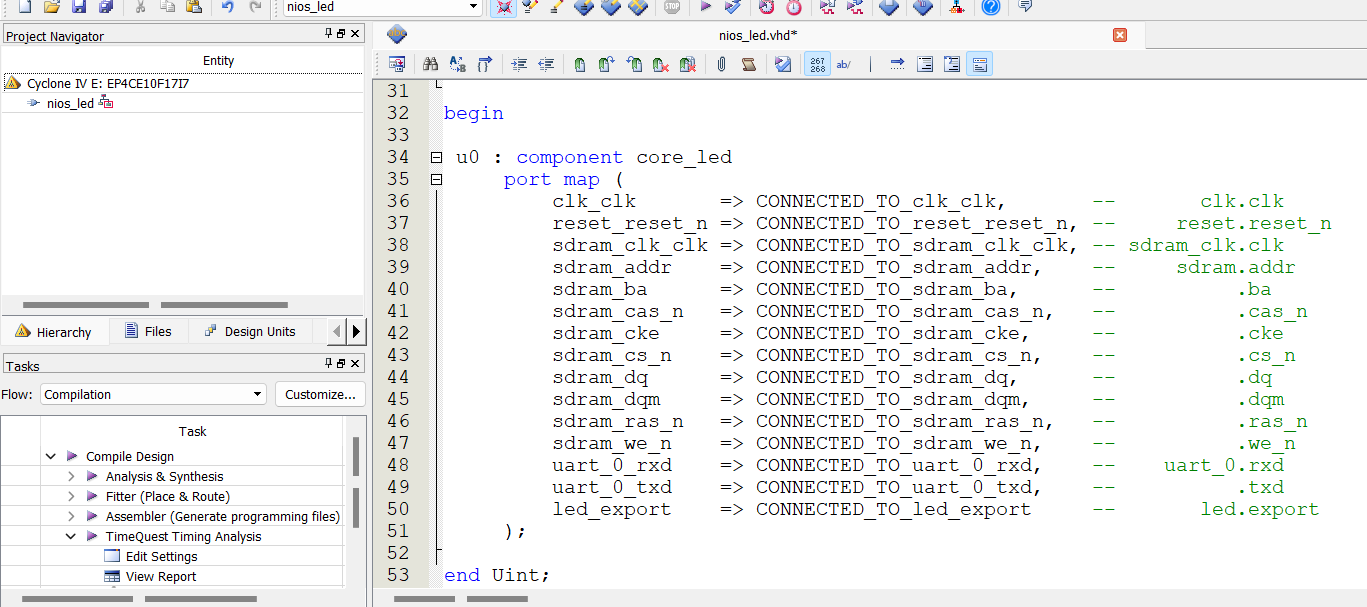

位置在begin之后,end之前。修改之前是这样:

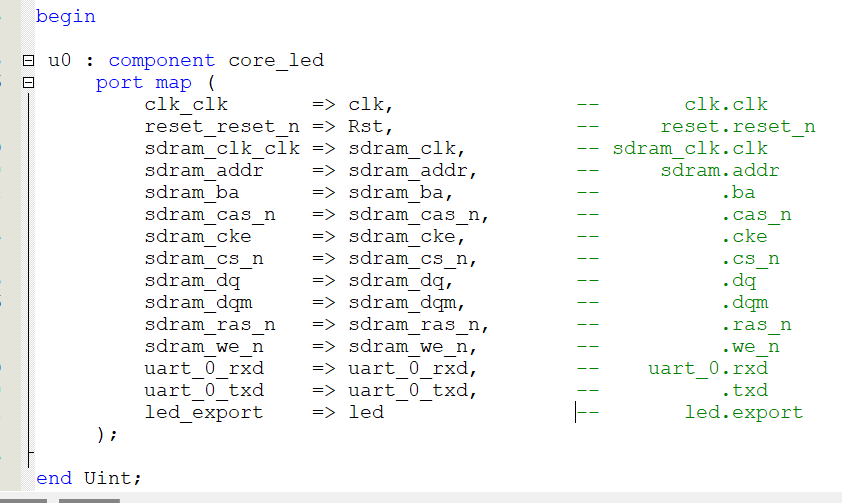

修改之后变成这样:

同时,刚刚创建的实体entity也需要进行修改。目的是把SDRAM的接口和LED的接口分配到FPGA上,具体哪个管脚先不用管。修改后如下:

至此,VHDL代码部分基本完成。

三、第一次编译

到这里,可以先进行一次编译。目的有两个,一个是看下有没有语法或配置的错误,另一个是为后面分配管脚做准备。

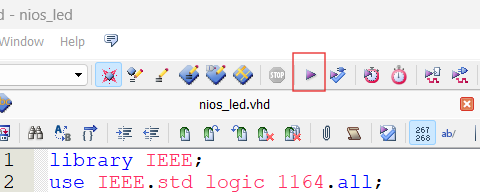

点击菜单栏上的Start Compilation,进行编译,如图:

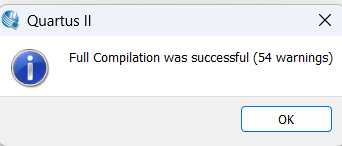

编译完成后,没有错误,有些警告。警告不影响,忽略即可。

这一节内容比较简单,我是单片机爱好者-MCU起航,打完收工!